香港科技大學的研究人員開發了一種新的集成技術,用於將III-V族化合物半導體器件與矽高效集成,為低成本、大容量、高速和高輸送量的光子集成提供了基礎,有助改革數據通信的發展。

有別於使用電子的傳統集成電路或微芯片,光子集成電路使用光子或光粒子。 光子集成結合了光和電子學以加速數據傳輸。 當中,矽光子學(Si-photonics)處於這場革命的最前沿,它能夠創建同時處理大量數據的高速、低成本連接。

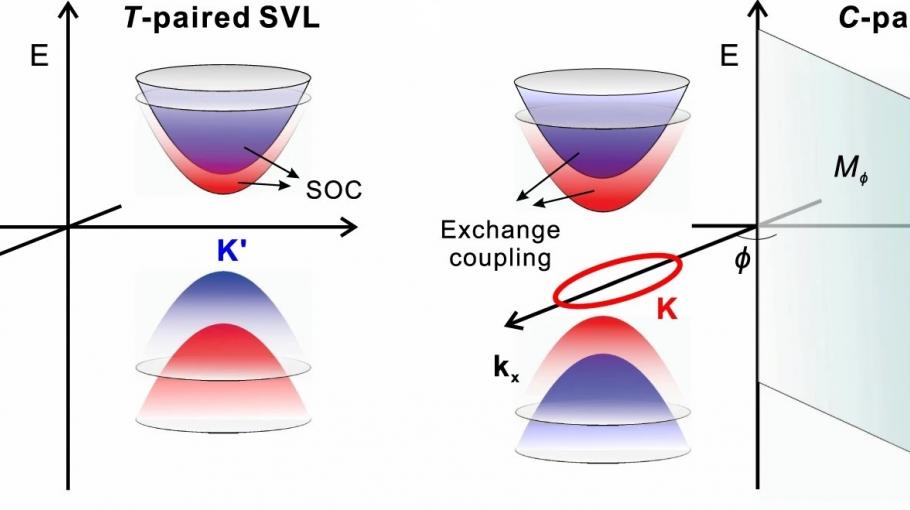

雖然矽能夠實現無源光學功能,但它難以實現有源功能,例如,生成光(鐳射器)或檢測光(光電探測器)——兩者都是關鍵的數據生成與讀出組件。 因此,需要將III-V族半導體(使用來自週期表第III族和第V族的材料)集成到矽襯底上,以實現完整的功能並提高效率。

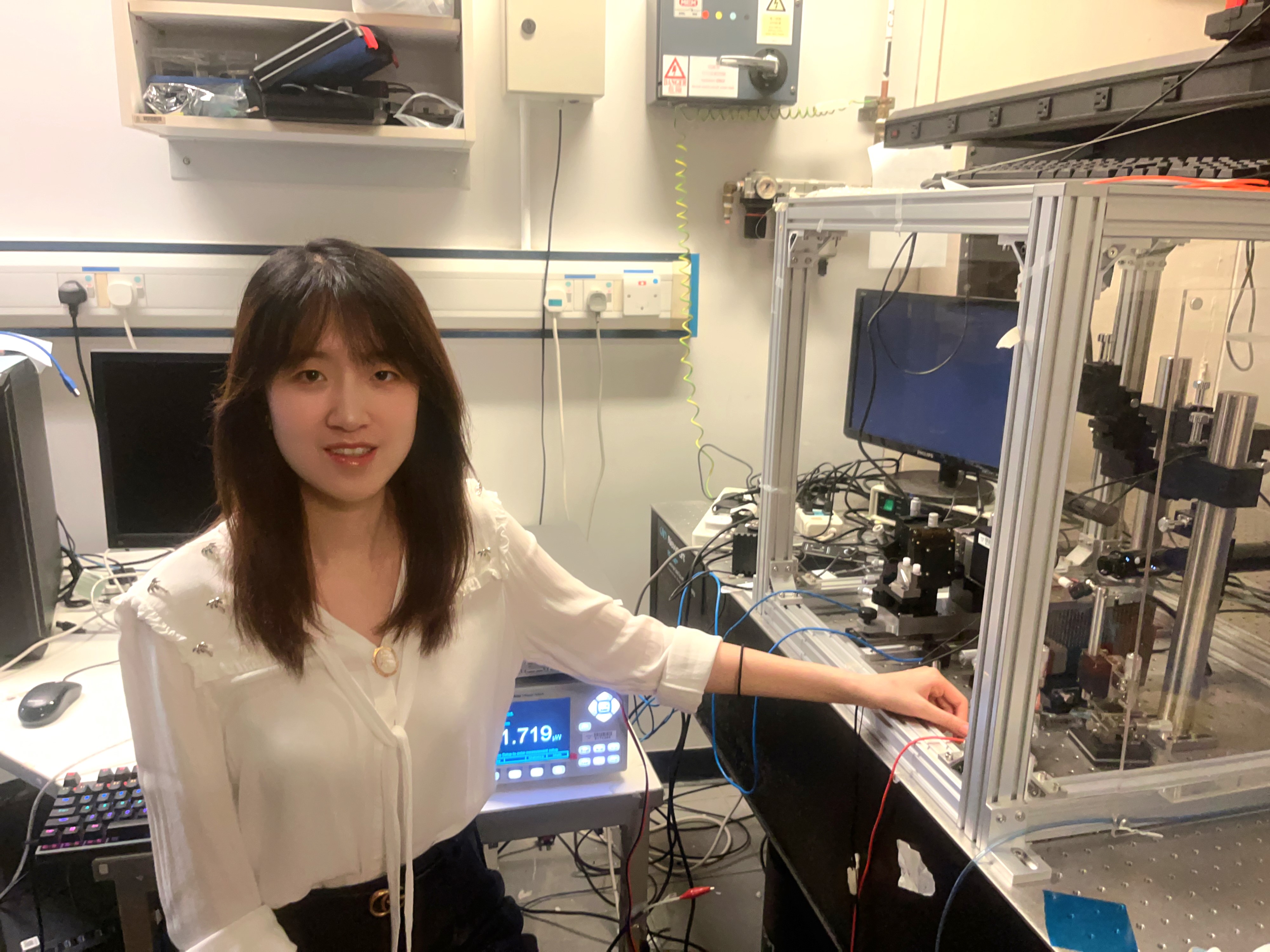

然而,儘管III-V族半導體能夠很好地完成有源功能,但它們無法自然地與矽結合。 在新興跨學科領域學部研究助理教授薛瑩和研究教授劉紀美的帶領下,研究團隊找到了一種能夠讓III-V族器件與矽高效結合的方法,從而解決了這項挑戰。

他們開發了一種名為橫向縱橫比捕獲(LART)的技術,這是一種新穎的選擇性直接外延法,可以在絕緣體上矽(SOI)上,橫向選擇性生長III-V族材料,而無需厚緩衝層。

儘管根據現有文獻,尚無任何集成方法能夠以高耦合效率和高產量方式來解決III-V族有源功能與矽無源功能結合這一挑戰,但團隊的LART方法有效地實現了面內III-V族鐳射器,從而使III-V族鐳射器與矽可以在同一平面內耦合,因而高效。

薛瑩教授指出:「我們的方案解決了III-V族器件與矽的失配問題。 該方案實現了III-V族器件的優異性能,讓III-V族與矽的耦合變得簡單高效。 」

過去幾十年,在大數據、雲應用和傳感器等新興技術的推動下,數據流量呈指數級增長。 積體電路(IC,也稱為微電子)技術通過縮小電子器件的尺寸並提高其運行速度,實現了符合摩爾定律(Moore’s Law)的指數級增長——微芯片上的晶體管數量大約每兩年翻倍。 然而,數據流量的持續爆炸性增長,已將傳統電子器件推到了極限。

2016年,澤字節時代開啟,數據的生成、處理、傳輸、存儲和讀出規模出現飛速增長。 數據規模的激增給速度、頻寬、成本和功耗方面帶來嚴峻挑戰。在此背景下,光子集成技術應運而生。

研究團隊計劃在後續研究工作中證明,與矽波導集成的III-V族鐳射器能夠發揮優異性能,例如,閾值低、輸出功率高、使用壽命長,並且能夠在高溫條件下工作。

薛教授補充,在這項技術應用於現實生活之前,還有一些關鍵性的科學挑戰需要解決。 然而,該技術將有望實現新一代通信,並推動各種新興應用和研究領域的發展——包括超級計算機、人工智能、生物醫學、汽車應用,以及神經和量子網路。

相應研究報告近期發表於《鐳射與光子評論》,並被選為封面。 此外,憑藉在相關工作中開發的新型外延技術和集成方案,薛教授榮獲2023 年國際光學學會(Optica)挑戰基金獎,以進一步推進這項研究工作。